Designing FPGA Tutorial

image

Welcome to Sven Andersson's blog

My name is Sven Andersson and Iwork as a consultant in embedded

system design, implemented in ASIC

and FPGA.

In my spare time I write this blog

and I hope it will inspire others to

learn more about this fantastic field.

I live in Stockholm Sweden and have

my own company...

Content

What's new

Starting a blog

Writing a blog

Using an RSS reader

Zynq Design From Scratch

Started February 2014

1 Introduction

Changes and updates

2 Zynq-7000 All Programmable SoC

3 ZedBoard and other boards

4 Computer platform and VirtualBox

5 Installing Ubuntu

6 Fixing Ubuntu

7 Installing Vivado

8 Starting Vivado

9 Using Vivado

10 Lab 1. Create a Zynq project

11 Lab 1. Build a hardware platform

12 Lab 1. Create a software application

13 Lab 1. Connect to ZedBoard

14 Lab 1. Run a software application

15 Lab 1. Benchmarking ARM Cortex-A9

16 Lab 2. Adding a GPIO peripheral

17 Lab 2. Create a custom HDL module

18 Lab 2. Connect package pins and implement

19 Lab 2. Create a software application and configure the PL

20 Lab 2. Debugging a software application

21 Running Linux from SD card

22 Installing PetaLinux

23 Booting PetaLinux

24 Connect to ZedBoad via ethernet

25 Rebuilding the PetaLinux kernel image

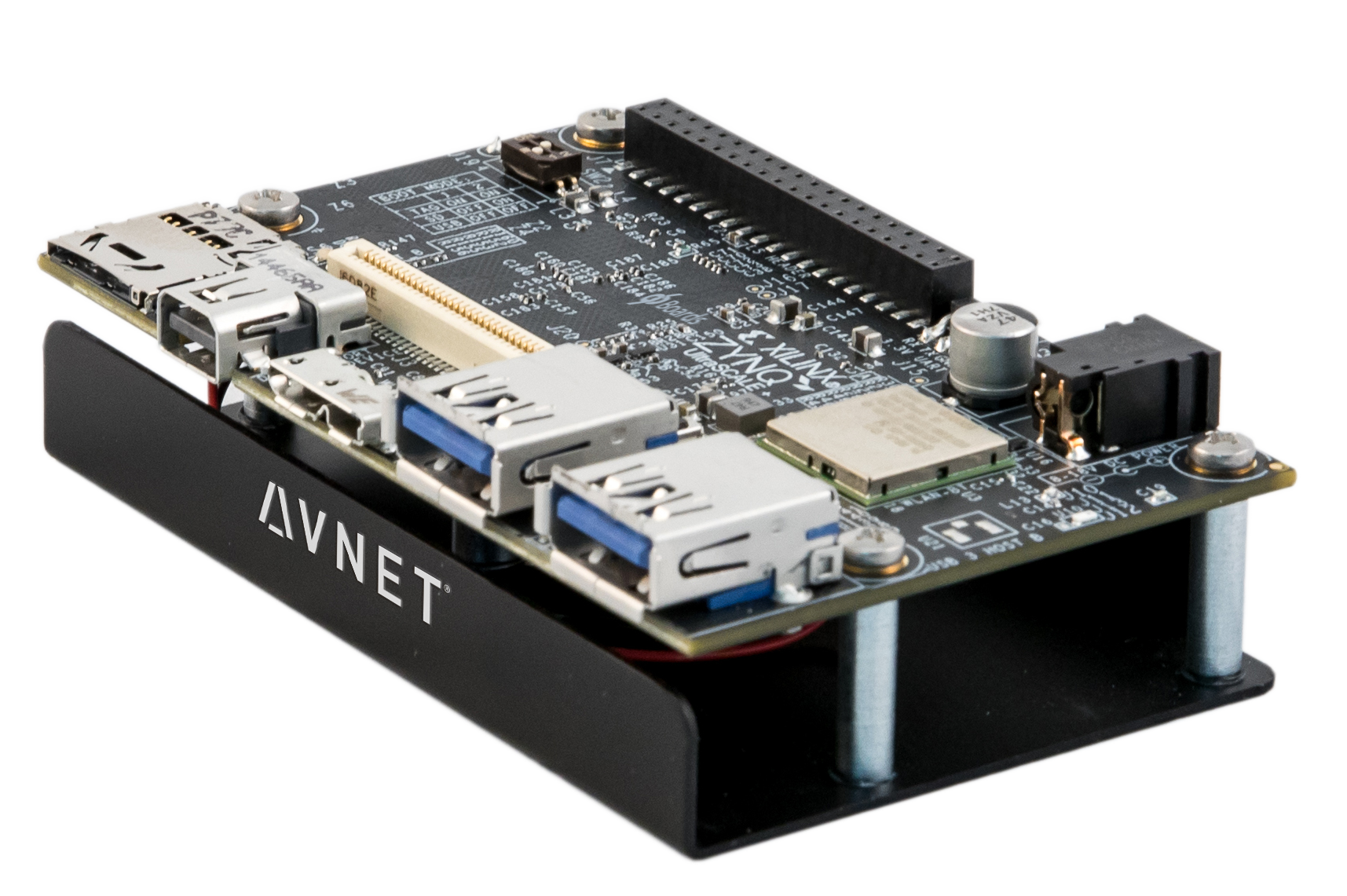

26 Running a DHCP server on the host

27 Running a TFTP server on the host

28 PetaLinux boot via U-boot

29 PetaLinux application development

30 Fixing the host computer

31 Running NFS servers

32 VirtualBox seamless mode

33 Mounting guest file system using sshfs

34 PetaLinux. Setting up a web server

35 PetaLinux. Using cgi scripts

36 PetaLinux. Web enabled application

37 Convert from VirtualBox to VMware

38 Running Linaro Ubuntu on ZedBoard

39 Running Android on ZedBoard

40 Lab2. Booting from SD card and SPI flash

41 Lab2. PetaLinux board bringup

42 Lab2. Writing userspace IO device driver

43 Lab2. Hardware debugging

44 MicroZed quick start

45 Installing Vivado 2014.1

46 Lab3. Adding push buttons to our Zynq system

47 Lab3. Adding an interrupt service routine

48 Installing Ubuntu 14.04

49 Installing Vivado and Petalinux 2014.2

50 Using Vivado 2014.2

51 Upgrading to Ubuntu 14.04

52 Using Petalinux 2014.2

53 Booting from SD card and SPI flash

54 Booting Petalinux 2014.2 from SD card

55 Booting Petalinux 2014.2 from SPI flash

56 Installing Vivado 2014.3

Chipotle Verification System

Introduction

EE Times Retrospective Series

It all started more than 40 years ago

My first job as an electrical engineer

The Memory (R)evolution

The Microprocessor (R)evolution

Four soft-core processors

Started January 2012

Introduction

Table of contents

Leon3

MicroBlaze

OpenRISC 1200

Nios II

Using the Spartan-6 LX9 MicroBoard

Started August 2011

Introduction

Table of contents

Problems, fixes and solutions

FPGA Design From Scratch

Started December 2006

Introduction

Table of contents

Index

Acronyms and abbreviations

Actel FPGA design

Designing with an Actel FPGA. Part 1

Designing with an Actel FPGA. Part 2

Designing with an Actel FPGA. Part 3

Designing with an Actel FPGA. Part 4

Designing with an Actel FPGA. Part 5

CAD

A hardware designer's best friend

Zoo Design Platform

Linux

Installing Cobra Command Tool

A processor benchmark

Mac

Porting a Unix program to Mac OS X

Fixing a HyperTerminal in Mac OS X

A dream come true

Bicycling

Stockholm by bike

Running

The New York City Marathon

Skiing/Skating

Kittelfjall Lappland

Tour skating in Sweden and around the world

Top

Introduction

SSSK

Wild skating

Tour day

Safety equipment

A look at the equipment you need

Skate maintenance

Links

Books, photos, films and videos

Weather forecasts

Travel

38000 feet above see level

A trip to Spain

Florida the sunshine state

Photo Albums

Seaside Florida

Ronda Spain

Sevilla Spain

Cordoba Spain

Alhambra Spain

Kittelfjäll Lapland

Landsort Art Walk

Skating on thin ice

Books

100 Power Tips for FPGA Designers

Favorites

Adventures in ASIC

ChipHit

Computer History Museum

DeepChip

Design & Reuse

Dilbert

d9 Tech Blog

EDA Cafe

EDA DesignLine

Eli's tech Blog

Embedded.com

EmbeddedRelated.com

FPGA Arcade

FPGA Blog

FPGA Central

FPGA CPU News

FPGA developer

FPGA Journal

FPGA World

Lesley Shannon Courses

Mac 2 Ubuntu

Programmable Logic DesignLine

OpenCores

Simplehelp

SOCcentral

World of ASIC