CryptoMining via FPGA's:

FPGA for Dummies & Experts Alike!

The ASICs had overtaking GPU mining, but an alternative to ASIC mining was born.

The new wolfpack leader appears as the Field Programmable Gate Arrays, or shortly FPGA and it is taking over very fast.

The only issue here is the boards are difficult to find each passing month.

Disclaimer: this post is not sponsored by any company nor have any referral links.

Let’s look at why FPGA is interesting for mining.

The Two Main Issues FPGA Are Meant to Solve Cryptocurrencies are volatile and unstable in the current market, August-2018.

Cryptocurrency market have been jumping from Ethereum to Monero to Zcash, back and forth, depending on the volatility of coin profitability.

The ASICs storming the mining pool strategy is to buy an ASIC miner and pray that it pays off in time. GPU mining and the amount of coins you can mine is limited and people find this unsatisfactory 75% of the time.

The ASIC's issue is it offers zero flexibility when it comes to a single coin that can be mined and no other type of cryptocurrency coin.

An ASIC is hard-wired to mine one algorithm type of coin only.

Highest End, Lowest Cost:

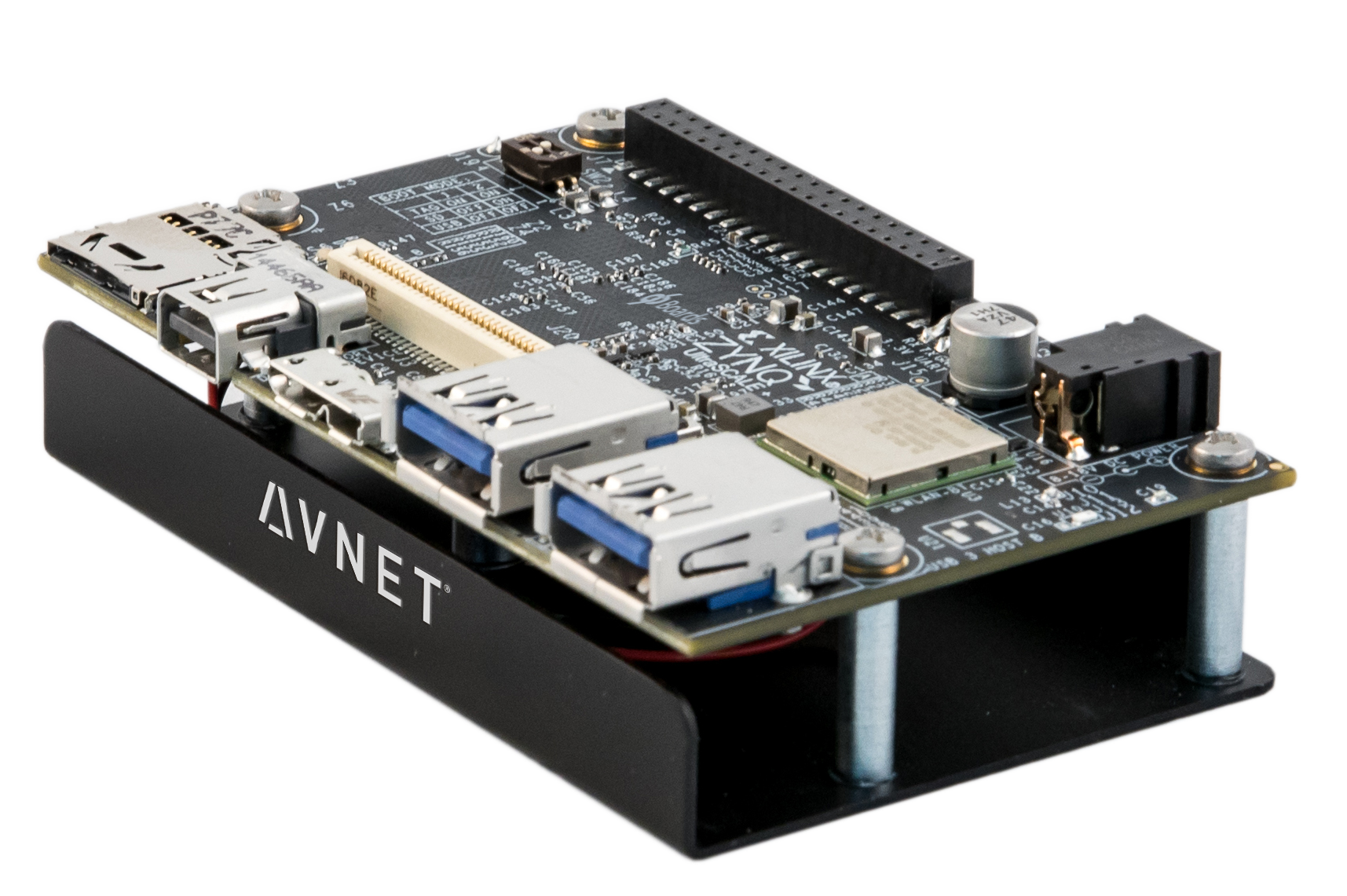

Ultra96 is an Arm-based, Xilinx Zynq UltraScale+ MPSoC development board based on the Linaro 96Boards specification.

The 96Boards’ specifications are open and define a standard board layout for development platforms that can be used by software application, hardware device, kernel, and other system software developers.

Ultra96 represents a unique position in the 96Boards community with a wide range of potential peripherals and acceleration engines in the programmable logic that is not available from other offerings.

Ultra96 boots from the provided Delkin 16 GB MicroSD card, pre-loaded with PetaLinux.

Engineers have options of connecting to Ultra96 through a Webserver using integrated wireless access point capability or to use the provided PetaLinux desktop environment which can be viewed on the integrated Mini DisplayPort video output.

Multiple application examples and on-board development options are provided as examples.

Ultra96 provides four user-controllable LEDs.

Engineers may also interact with the board through the 96Boards-compatible low-speed and high-speed expansion connectors by adding peripheral accessories such as those included in Seeed Studio’s Grove Starter Kit for 96Boards.

Micron LPDDR4 memory provides 2 GB of RAM in a 512M x 32 configuration. Wireless options include 802.11b/g/n Wi-Fi and Bluetooth 4.2 (provides both Bluetooth Classic and Low Energy (BLE)).

UARTs are accessible on a header as well as through the expansion connector. JTAG is available through a header (external USB-JTAG required). I2C is available through the expansion connector.

Ultra96 provides one upstream (device) and two downstream (host) USB 3.0 connections. A USB 2.0 downstream (host) interface is provided on the high speed expansion bus.

Two Microchip USB3320 USB 2.0 ULPI Transceivers and one Microchip USB5744 4-Port SS/HS USB Controller Hub are specified.

The integrated power supply generates all on-board voltages from an external 12V supply (available as an accessory).

What’s the Third Option: There is always other option$.

FPGA is the hardware taking over the market by storm. This is the new favorite in the cryptocurency mining community.

FPGA have been around since 1979.

They heavily used in science, vehicle modeling and even military deployment applications.

The first manufacturer of these devices is an American technology company called "Xilinx".

Years followed and another American company called Altera, (now owned by Intel), has joined the industry and has been the main Xilinx competitor since then.

The development of FPGA circuitboards have been welcomed very in many industries and the demand FPGA hardware technology is still booming.

In 2013, the market for FPGA circuit boards was $6.1 billion and estimated $21.3 billion by year 2020.

Why FPGA Have not been used in cryptocurrency mining:

Since Bitcoin became popular, average people tried to mine with FPGA, but failed because they did not have the programming skill sets to utilize the FPGA circuit-boards.

The only people have mined FPGA circuit-boards were large mining exchanges, and they kept the FPGA circuit boards a secret for years.

When the first open source FPGA Bitcoin miner was released from private sectors until May 20, 2011.

Juan Antonio Ernesto's Great Adventure:

A man named Juan Antonio Ernesto's, [his named was changed here to protect his immigration innocence], from Tijuana Mexico, who illegally migrated into Canada from Mexico, and was hired by Canada's silicon-valley, (in Waterloo Ontario).

After three years Juan left Canada, because of bias Canadian in that country, so Juan Antonio said, he had to leave to U.S..

When Juan entered the U.S. he was immediately granted citizenship by the U.S. government, because enrolled into U.S. college for free and acquired his CS-masters degree from NMT Socorro New-Mexico under his real name.

While he was in Socorro NM he and other Mexicans-Americans secretly managed the cryptocurrency mining software exchanged named "Macho-Rio-Grande".

The Mexican trio enabled the FPGA Xilinux cards workable and online usable for cryptocurrency mining.

The trio secretly made millions of dollars and they were the only private-public sector aware of this technology.

When Juan returned with millions of dollars of wealth to share with his friends in Canada he died from a fatal gunshot wound by MS13 in Vancouver Canada on the highway of tears.

Juan's bank accounts and cryptocurrencies was transferred before his death never to be found again.

Juan's friends ran to Mexico with the FPGA software technology and where also found dead months later and their accounts where all transferred the same.

All deaths related to these events where determined suicide, and the mystery of their deaths continues as everyone suspects MS13 hackers.

NOW, there are three reasons why FPGA circuit-boards have never really made it to the masses until today and the above mentioned is the first.

The Reason #1, is the lacking of non-programmable flexibility and software to architecture specifics.

FPGA boards are not easy to software program, and they can be programmed to mine cryptocurrency.

In order to use a FPGA board you must have hardware and software programming abilities.

The GPU works differently and the only changes enabled is to tweak the clock speed, and mining software.

The FPGA circuit-board has got to be programmed in raw-code from scratch in order to mine cryptocurrency. Writing the code in Verilog or VHDL language -and– neither Python nor C++ works, but only Verilog or VHDL languages.

Only dedicated programmers are capable managing this task from beginning equation to end resolved solution.

The Reason #2, is the creation of the first ASIC for mining cryptocurrencies, Unlike FPGA, was an ASIC hard-coded as a plug and play hardware only and not reprogrammable.

Anyone can use an ASIC Miner-Box. There were a lot of alternatives to ASIC mining-box. Computer programmers have had the option of the GPU rigs and resolved into mining lesser coins than an FPGA circuit-board capable of.

The ASIC miner-box's are dominating the mining pools and Personal Computer Graphic Card GPU's are now less used technology.

The FPGA are becoming the average miner hardware these days.

There are several reasons FPGA are way faster.

The FPGA circuit-board cards perform 3x to 100x times more efficient than GPU while having the same wattage power voltage draw saving hundred$.

Depending on the algorithm matched to bitcoin, FPGA never fall behind ASICs miner-box's.

Upsides of FPGA

+ Compatibility for all mining currencies provided you are a flexibility with Verilog or VHDL programming languages, or have partnered up with a programmer regards all cryptocurrency mining algorithms. There are no soft-forks affecting mining operations provided the programmer updates FPGA bitstream.

+ Extreme power efficiency compared to CPU's and GPUs.

Downsides of FPGA

+ FPGA have to be plugged into operational computers, just like GPUs.

+ Xilinux Vertex FPGA available to the mainstream for now (there are some exceptions though, which is why this article exists, more on that below).

+ Are quite pricey compared to GPUs.

+ Can be slightly outperformed by ASICs depending on the algorithm.

Bitstream:

The Bitstream is the program written on a low-level programming language known as Verilog or VHDL that tells the FPGA what to do.

If you want to mine a specific algorithm you must have a bitstream that tells the FPGA how to mine that specific algo.

Bitstreams are loaded to the FPGA once the system boots. The bitstream is loaded into the volatile FPGA RAM memory. This is the same DDR4 memory – the FPGA model people use for mining has got 64GB of it.

This huge amount of RAM allows the FPGA to store hundreds of bitstreams and switch between those in fractions of a second.

This functionality allows an FPGA to mine algorithms such as Timetravel10, X11Evo, X16R and X16S that require the chip to switch between various “lesser” hashing algorithms every few minutes.

While the bitstream can be changed in a fraction of a second, the board can still mine only one algorithm at a time with a couple rare exceptions.

Anyone can create bitstreams for existing mining algos and Zetheron (name of the company) will be collecting a fixed fee on behalf of the developers. This will ensure:

safety to the developers of bitstreams – they will get paid for their work and

no entry fee for FPGA owners – you pay only if the bitstream you have downloaded works

Plus, the access to a diversity of community-made bitstream will certainly guarantee that we will be able to mine virtually any algo and fork we want.